# go2async: A High-Level **Synthesis Tool for Asynchronous Circuits Based on Click-Elements**

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

# **Technische Informatik**

eingereicht von

# Sebastian Michael Wiedemann, BSc

Matrikelnummer 01425647

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Mitwirkung: Dipl.Ing. Dipl.Ing. Dr.techn. Jürgen Maier, BSc

Univ.Ass. Dipl.-Ing. Dr.techn. Florian Ferdinand Huemer, BSc

| Wien, 26. September 2023 |                             |                    |

|--------------------------|-----------------------------|--------------------|

|                          | Sebastian Michael Wiedemann | Andreas Steininger |

# go2async: A High-Level **Synthesis Tool for Asynchronous Circuits Based on Click-Elements**

# **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

# **Diplom-Ingenieur**

in

# Computer Engineering

by

# Sebastian Michael Wiedemann, BSc

Registration Number 01425647

to the Faculty of Informatics

at the TU Wien

Advisor: Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Andreas Steininger Assistance: Dipl.Ing. Dipl.Ing. Dr.techn. Jürgen Maier, BSc

Univ.Ass. Dipl.-Ing. Dr.techn. Florian Ferdinand Huemer, BSc

| Vienna, 26 <sup>th</sup> September, 2023 |                             |                    |

|------------------------------------------|-----------------------------|--------------------|

|                                          | Sebastian Michael Wiedemann | Andreas Steininger |

# Erklärung zur Verfassung der Arbeit

Sebastian Michael Wiedemann, BSc

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 26. September 2023

Sebastian Michael Wiedemann

# Danksagung

An diesem Punkt bedanke mich herzlichst bei meinen Betreuern Andreas Steininger, Florian Huemer und Jürgen Maier, die mich während der Erstellung meiner Diplomarbeit begleitet haben. Mit regelmäßiger konstruktiver Kritik haben sie mich großartig und essenziell unterstützt. Natürlich dient mein Dank auch meinen Studienkolleg:innen, mit denen ich über viele Studienjahre einen prägenden Teil meines Lebens verbringen durfte. Außerdem möchte ich tiefe Dankbarkeit meinen Eltern aussprechen, die mir mein Studium ermöglicht haben, sowie meinen Geschwistern und Verwandten, die mich stets motivierten. Sie, mein innerer Freundeskreis und meine Partnerin verdienen eine besondere Erwähnung: Danke für das rege Feedback, die Übersetzungs- und Formulierungshilfen sowohl für die Feiern und die schöne Zeit.

# Acknowledgements

At this point, I would like to express my sincere thanks to my supervisors Andreas Steininger, Florian Huemer and Jürgen Maier, who accompanied me during the creation of my thesis. With regular constructive criticism they have given me great and essential support. Of course, I would also like to thank my fellow students, with whom I was able to spend an important part of my life over many years of study. I would also like to express my deep gratitude to my parents, who made my studies possible, as well as to my siblings and relatives, who have always motivated me. They, my inner circle of friends and my significant other deserve a special mention: thank you for the lively feedback, the translation and formulation help as well as for the parties and the good times.

# Kurzfassung

Wir haben bereits die Sub-5nm-Technologie für Halbleiterschaltungen erreicht und scheinen die physikalischen Grenzen der kleinstmöglichen Transistorgrößen zu erreichen. Um die Leistung von Computersystemen weiter zu steigern, kann versucht werden, spezielle Hardware für bestimmte Softwareaufgaben zu entwickeln, um diese zu beschleunigen. Dies ist eine äußerst riskante Aufgabe, da der Entwurfsprozess sehr kostspielig und zeitaufwändig ist. Der Einsatz von FPGAs und die Verwendung formaler Beschreibungen in Form von HDLs erleichtern diesen Prozess. Eine zusätzliche Abstraktionsebene und HLS-Tools ermöglichen es sogar, dass Nicht-Hardware-Spezialist:innen Schaltungen zur Beschleunigung von Computeraufgaben entwickeln können.

Grundsätzlich gibt es zwei Arten von digitalen Schaltungen: synchrone und asynchrone. Synchrone Schaltungen stellen die alltägliche Hardware dar. Ein globaler Taktgeber steuert eine Schaltung und bestimmt die Arbeitsgeschwindigkeit. Asynchrone Schaltungen haben vielversprechende Vorteile im Vergleich zu ihrem getakteten Gegenstück in Bezug auf Leistungseffizienz und physikalische Anpassungsfähigkeit. Der Entwurf von Schaltungen ohne Taktgeber ist jedoch weitaus schwieriger und wird oft als nicht machbar angesehen, sofern keine technischen Hilfsmittel zur Verfügung stehen.

Um dieses Problem in Angriff zu nehmen, wird in dieser Masterarbeit ein HLS-Tool für asynchrone Schaltungen entwickelt: go2async. Go2async ist ein HLS-Tool, welches eine Teilmenge der bekannten Programmiersprache Go parst. Die Hardware basiert auf dem Prinzip der Syntaxbaum-gerichteten Übersetzung. Die erzeugte Hardware ahmt die Funktionalität der Eingabesoftware nach und basiert auf vorverifizierten Click-Element-Strukturen, die speziell mit Blick auf FPGAs entwickelt wurden. Go2async ermöglicht es Go-Softwareentwickler:innen asynchrone Hardware zu erstellen, ohne viel Wissen über die Entwicklung asynchroner Hardware zu benötigen.

Das vorgeschlagene HLS-Tool generiert VHDL-Code, das es ermöglicht, die erzeugten asynchronen Schaltungen mit typischen Simulationsprogrammen zu simulieren. Diese Masterarbeit verifiziert die generierten asynchronen Schaltungen mit Hilfe von ausgewählten Eingabe-Funktionen und zeigt, dass go2async in der Lage ist, automatisch und erfolgreich asynchrone Schaltungen auf Basis von Click-Element-Strukturen zu generieren. Zusätzlich, ist es für gängige Synthesewerkzeuge möglich, laufbare Hardware für FPGAs zu erstellen, wodurch die Nutzung der von go2async generierten asynchronen Hardware in einem realen Szenario ermöglicht wird.

# Abstract

We have already reached the sub 5nm technology for semiconductor circuits and seem to reach physical limits on smallest possible transistor sizes. To further increase computer system performance, we can try to create dedicated hardware for specific software tasks to speed them up. This is an enormously risky task since the design process is very costly and time-sensitive. The usage of FPGAs eases this problem by using HDLs to formally describe hardware and allowing virtual prototyping. By using an additional abstraction layer and HLS tools it is possible to enable non hardware-specialists to create hardware to speed up computer tasks.

There are basically two types of digital circuits: synchronous and asynchronous. Synchronous circuits represent the everyday hardware. A global clock governs a circuit and determines the operating speed. Asynchronous circuits have promising benefits in comparison to its clocked counterpart in regards to power efficiency and physical adaptability. However, the design of clock-less circuits is way harder and often considered unfeasible without tool support.

To tackle this problem, this thesis proposes a HLS tool for asynchronous circuits: go2async. Go2async is an HLS tool that parses a subset of the well-known programming language Go. The hardware creation is based on a syntax tree directed translation principle. The created hardware mimics the functionality of the input software and is based on preverified click-element structures which were specifically designed with FPGAs in mind.

Go2async enables Go software developers to create asynchronous hardware without needing much knowledge about the asynchronous design process. The proposed HLS tool generates VHDL code which makes it possible to simulate generated asynchronous circuits with typical simulation programs. The thesis verifies generated asynchronous circuits with the help of selected input functions and shows that go2async is able to automatically and successfully generate asynchronous circuits based on click-element structures. Additionally, it is possible for common synthesis tools to create downloadable hardware for FPGAs thus enabling usage of go2async's generated asynchronous hardware in a real world scenario.

# Contents

| Kurzfassung  |       |                                                |      |  |  |  |

|--------------|-------|------------------------------------------------|------|--|--|--|

| $\mathbf{A}$ | bstra | act                                            | xiii |  |  |  |

| C            | onter | nts                                            | xv   |  |  |  |

| 1            | Intr  | roduction                                      | 1    |  |  |  |

|              | 1.1   | Motivation                                     | 2    |  |  |  |

|              | 1.2   | Problem Description                            | 2    |  |  |  |

|              | 1.3   | Research Questions & Expected Results          | 3    |  |  |  |

|              | 1.4   | Methodological Approach                        | 3    |  |  |  |

|              | 1.5   | Structure of this Work                         | 4    |  |  |  |

| 2            | Met   | thodology                                      | 7    |  |  |  |

| 3            | Tec   | hnical Background                              | 11   |  |  |  |

|              | 3.1   | Synchronous Circuits                           | 11   |  |  |  |

|              | 3.2   | Asynchronous Circuits                          | 12   |  |  |  |

|              | 3.3   | High-Level Synthesis Tools                     | 15   |  |  |  |

|              | 3.4   | Asynchronous Pipelines                         | 16   |  |  |  |

|              | 3.5   | Work on Click-Elements                         | 20   |  |  |  |

|              | 3.6   | Conclusion of Pipeline Findings                | 21   |  |  |  |

|              | 3.7   | Programming Language Candidates                | 22   |  |  |  |

| 4            | Key   | Challenges and Solution Concepts               | 25   |  |  |  |

|              | 4.1   | Key Challenges                                 | 25   |  |  |  |

|              | 4.2   | Solution Concepts                              | 26   |  |  |  |

| 5            | Imp   | Implementation                                 |      |  |  |  |

|              | 5.1   | Program Execution                              | 35   |  |  |  |

|              | 5.2   | The Supported Go Subset                        | 36   |  |  |  |

|              | 5.3   | Abstraction of Resulting Asynchronous Circuits | 38   |  |  |  |

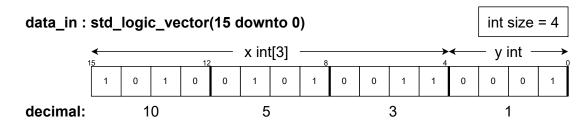

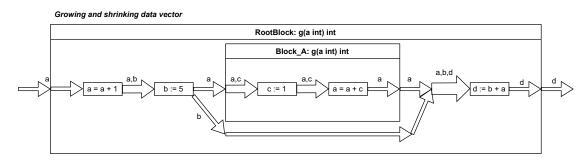

|              | 5.4   | Data Structures                                | 40   |  |  |  |

|              | 5.5   | Variable Handling                              | 46   |  |  |  |

|              |       |                                                |      |  |  |  |

|                 | 5.6      | Handshake Connection handling             | 48 |  |  |  |

|-----------------|----------|-------------------------------------------|----|--|--|--|

|                 | 5.7      | Parsing Go with the built-in Go AST       | 52 |  |  |  |

|                 | 5.8      | Hardware Generation                       | 53 |  |  |  |

|                 | 5.9      | Generation Example                        | 54 |  |  |  |

| 6               | Sim      | ulation & Exploration of Limits           | 59 |  |  |  |

|                 | 6.1      | Testing Requirements                      | 59 |  |  |  |

|                 | 6.2      | Simulation Workflow                       | 60 |  |  |  |

|                 | 6.3      | Exhaustive Simulation                     | 63 |  |  |  |

|                 | 6.4      | The High-Level Synthesis Tool in Practice | 66 |  |  |  |

|                 | 6.5      | Limits of go2async                        | 68 |  |  |  |

| 7               | Opt      | imization & Design Decisions              | 71 |  |  |  |

| •               | 7.1      | The Initial Solution                      | 71 |  |  |  |

|                 | 7.2      | Array Support                             | 73 |  |  |  |

|                 | 7.3      | Recursive Blocks                          | 75 |  |  |  |

|                 | 7.4      | Calling Functions                         | 75 |  |  |  |

|                 | 7.5      | Nested Binary Expressions                 | 76 |  |  |  |

|                 | 7.6      | Optimizing Variable Handling              | 76 |  |  |  |

|                 | 7.7      | Introduction of the Dataflow Model        | 78 |  |  |  |

| 8               | Cor      | aclusion & Outlook                        | 81 |  |  |  |

| Ü               | 8.1      | Future Work                               | 82 |  |  |  |

| т.              | , ,      |                                           | 85 |  |  |  |

| List of Figures |          |                                           |    |  |  |  |

| A               | Acronyms |                                           |    |  |  |  |

| Bibliography    |          |                                           |    |  |  |  |

CHAPTER.

# Introduction

The never ending urge for increased circuit performance while maintaining power, resource, and cost efficiency will remain a challenge for the hardware industry [1, 2]. When looking at the specifications of a computer they usually include data about its processing core: the Central Processing Unit (CPU). Usually, there is a clock frequency associated with the CPU that essentially determines the speed of the whole system (e.g. [3]).

However, questions whether a circuit really needs a clock and whether the clock signal is necessary quickly arise. In fact, clock-less circuits, formally known as asynchronous circuits, do exist. Generally, the clock frequency of synchronous circuits governs the maximum time a signal can traverse through computation logic between flip-flops. The asynchronous counterpart is able to operate without the toggling clock signal by employing certain communication protocols between operation components (e.g. handshaking) [4].

Typical hardware structures contain some sort of pipeline. Instead of hardware solving a problem in its entirety at once, so-called pipeline stages allow hardware to perform calculations step-by-step. In synchronous circuits, a pipeline stage typically consists of logic between two flip-flops. The slowest pipeline stage determines the speed of the whole circuit. Usually, pipeline stages can be executed in parallel. A classic example of this structure can be seen in CPUs [5]. A high-performance CPU is able to simultaneously fetch a new instruction while the next pipeline stage can decode the previously fetched instruction.

The asynchronous sibling relies on specific hardware structures to employ similar pipelining capabilities which operate on a specific communication protocol. The click-element design template is an example implementation style for data-driven circuits [6] which are able to deploy pipelined asynchronous circuits operating step-by-step.

#### 1.1 Motivation

Synchronous circuits are basically everywhere with new hardware based on this communication style being released frequently. At a first glance, their counterpart, asynchronous circuits, are basically unheard of in the mainstream and seems like a research-only field with numerous advantages that come with a great price. However, on a closer look asynchronous circuits were always vaguely in the back of the head of the industry. Power efficiency, neuromorphic computing, and generally event-driven circuits given by the rising neural network research field gave this type of circuit another attention spike (e.g. IBM's TrueNorth [7] and Intel's Loihi [8]).

The work of [9, 10] shows that asynchronous hardware can be constructed by using standard library components. This is ideal for Field Programmable Gate Array (FPGA) implementations and thus enables simple testing of asynchronous circuits on broadly available FPGA development boards. However, generating asynchronous circuits based on click-elements is still a very cumbersome task to do manually. This is where the idea of a High-Level Synthesis (HLS) tool for this type of circuit came into fruition.

## 1.2Problem Description

Creating hardware to speed up certain software tasks is accompanied with a huge overhead, especially in verification. The design flow from the specification of hardware to an Application Specific Integrated Circuit (ASIC) is risky in regards to design, time to market, and market adoption. In general, ASIC designs are very cumbersome and cost extensive [11]. This makes custom hardware only advantageous if large quantities are needed.

A solution to this problem is using Hardware Description Languages (HDLs) (e.g. Verilog or Very High Speed Integrated Circuit Hardware Description Language (also VHDSIC) (VHDL)) to formally describe hardware. This enables the creation of virtual prototypes which can be simulated and tested virtually. If simulation results are satisfactory, it is possible to load the tested hardware into an FPGA such that a circuit can be tested physically. Besides creating a more convenient dynamic workflow this approach has numerous cost saving aspects in comparison to creating and testing circuits with many iteration cycles of ASICs.

However, the HDL approach still comes with a very complex design effort as well as an extensive verification process and requires specially trained personnel. This problem is hugely magnified when dealing with asynchronous circuits because the management of every single communication channel between components is required. This makes the manual design of large asynchronous circuits completely unfeasible without tool support.

## Research Questions & Expected Results 1.3

The overall goal of this thesis is to reduce the complexity of hardware generation. In that regard this project focuses on asynchronous circuits specifically. The main objective is to create a HLS tool that allows untrained personnel to quickly create asynchronous circuits without needing to know much about asynchronous circuits themselves.

To be more precise, the result of this theses shall be the HLS tool called qo2async written in the Go programming language [12] which parses a subset of Go itself with the help of the built-in Go parser and Go Abstract Syntax Tree (AST). The supported subset of Go consists of multiple sequentially occurring statements including common program flow structures such as if-statements and for-loops as well as nested code scopes (block statements). Other supported programming statements include arithmetic and binary expressions as well as function calls. To ensure a degree of simplicity only binary and integer variable types are allowed. Fixed size arrays can be used to ensure the usefulness of the high-level synthesis tool.

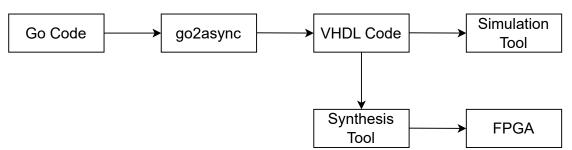

The program takes Go functions as inputs and generates synthesizeable VHDL code based on click-elements [9]. The resulting circuit functionally behaves the same as the input functions. The function parameters are the inputs of the resulting components and the function return variables are the circuit's output. The previously mentioned function call feature additionally enables interoperation with external circuits. The workflow concept is illustrated in Fig. 1.1.

Figure 1.1: Workflow concept of go2async.

To achieve its goal, the thesis has to address following research questions:

- Is it possible to synthesize click-based asynchronous hardware from a high-level design description in Go?

- How must the used capabilities of Go be restricted to keep the code synthesizable?

- Which measures can be taken to synthesize efficient asynchronous hardware?

## Methodological Approach 1.4

The methodological approach of this thesis consists of the following steps:

1. Problem description and extraction of challenges:

The first phase of this thesis involves the problem description. From there various challenges are directly implied which will be tackled in the subsequent steps and later chapters.

## 2. Literature study:

In the state of the art phase a review and analysis of related works and relevant literature will be done to build a knowledge base and provide background context for the work done in this thesis.

3. Exploration of existing options:

Here the results of the literature study will be discussed. In this step the thesis will construct some design ideas.

# 4. Implementation:

The largest chapter will cover the implementation of the hardware generator. The high-level synthesis tool is actually implemented in this step. The implementation decisions, explanations, discussions and justifications are covered.

5. Assessment of the implemented concept and exploration of limits by simulation and analysis:

In the simulation phase a specific state of the developed tool is analyzed. This will be mostly done by applying certain testcases and monitoring testbenches to verify generated hardware. Additionally, tool outputs will be synthesized on FPGAs and thus even tested physically and practically to ensure usefulness.

6. Optimization and re-evaluation:

The last step of this thesis covers the optimization of the tool. Here the results from the previous phase are evaluated. Depending on the requirement satisfaction status the resulting feedback is collectively applied back to phase 4 restarting an implementation cycle. This can either directly result in the optimization of previously programmed concepts or spring a new feature idea.

The plan is to start with a lightweight version of the tool, which can be improved one step at a time. Especially points 4 and onward can occur in repeating iterations with feedback-loops. This results in a more structured approach and thus yields easier verification.

#### 1.5 Structure of this Work

Chapter 1 presented an introduction for the work of this thesis, containing the motivation, problem description, expected results, as well as a teaser of the methodology which is more thoroughly discussed in Chapter 2. The literature review is covered in Chapter 3

which covers circuit types in more detail, related works, and useful background knowledge. Chapter 4 extracts challenges to be solved as well as drafts solution concepts for identified problems.

The practical part of the thesis starts with the implementation and inner workings of go2async explained in detail in Chapter 5. The thesis continues by showing simulations and verifies go2async's generated hardware by looking at a few examples before showcasing physically used circuits on an FPGA. The chapter ends by naming a few hardware and input software limits go2async has to deal with. The practical part of this thesis ends with Chapter 7 by covering different major versions of the asynchronous HLS tool implemented in this project starting with the initial solution which served as a proof of concept and baseline. Subsequent versions, new features, and ideas are covered here until arriving at the final version of this thesis' project. The thesis ends by summarizing the completed project and stating an outlook as well as ideas for future work in Chapter 8.

# Methodology

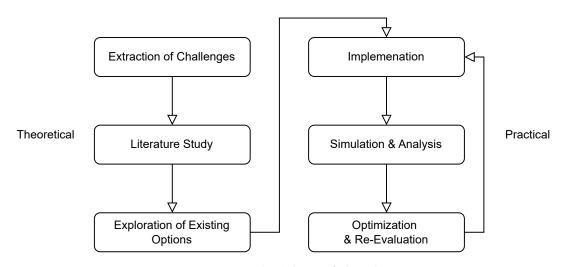

The applied methodology of this thesis can be seen in Fig. 2.1.

Figure 2.1: Methodology of this thesis.

It consists of the following six phases:

# 1. Problem description and extraction of challenges:

In the beginning phase of this thesis, the problems are described and the main challenges are extracted from there. Challenges will mainly be directly implied from the defined problems in the field. These can have a wide variety of complexity. One or more solution approaches will be formed for each challenge which will be handled in the later stages of this thesis.

Generally, the tackling of these challenges will be preceded by discussions. The purpose of the discussions is to find alternatives, analyze trade-offs and find the best path leading to the desired solutions. The main goal is to be able to justify the final approaches.

# 2. Literature study:

This part of this thesis will explore the current state of the art. The corresponding chapter will establish a knowledge base and gather the needed technical background to better understand the subject related to this work.

More precisely, the literature review will first introduce a discussion about synchronous vs. asynchronous circuits. Especially the drawbacks and known pitfalls of the well known synchronous space will be laid open, as well as how asynchronous circuits can solve various problems while introducing completely different complications and why it might be useful to study asynchronous circuits more thoroughly.

The field of related high-level synthesis tools for both circuit types is explored mentioning the benefits of using such programs. The general purpose behind such tools is explained. A few practical examples and their usages in the industry will be shown.

The title of this thesis reveals a focus on asynchronous circuits which of course implies that relevant and important circuit structures of this field are also discussed, namely asynchronous pipelines.

Related projects working on click-elements [9] will be reviewed which might be useful for implementation approach decisions later on and might even be relevant for comparisons or to draw parallels.

Since at the core of this thesis lies a software project the remaining puzzle piece before the development can start is finding a suitable programming language. Thus this chapter concludes by reviewing possible programming language candidates.

## 3. Exploration of existing options:

The findings of the previous phase will be discussed in this step. The assessment of the literature will not be its own chapter in this thesis. It will take place in a paragraph after findings and at the end of the relevant sections and subsections.

First design decisions and project ideas will be formed here. This includes the reasoning on click-elements as choice in the field of asynchronous pipelines and the two implementation concepts namely sequential vs. dataflow operation processing.

The discussion about the chosen programming language for this software project takes place in this chapter. Especially why the final decision was made in favor of

This part of the thesis concludes with the analysis of the Go AST and the clickelement structures from the click-library [10]. In particular certain patterns and possible parallels are searched which is required for the implementation part.

# 4. Implementation:

The implementation will be split into two different branches based on operation processing. The first and simpler branch involves the sequential execution of the instructions as defined in order by the code. This branch will be called sequential branch.

The second significant branch of this project involves dataflow processing. Here instructions and data-independent code-blocks are allowed to be executed in parallel. This branch will be called dataflow branch.

The project starts with the implementation of the sequential branch. Mainly because this will be much easier and straight forward since this is how single-threaded code is executed and the reference work done on click-elements [10] is based on this instruction processing style.

In the best case scenario the processing of the input code should work the same in both branches. The big difference will be the internal processing of data dependencies and component wirings.

Initially, the plan is to start small and gradually make the generator better and more powerful. After the study of the Go AST and found click-element patterns the choice of data structures and handling of component handshakes as well as data-connections will be crucial. The plan is to have easily expandable code in regards to the supported Go input code. Newly supported inputs should mainly not affect previously supported implementation structures. This should make the project seem brick-like where newly added features are independent bricks just added to the program whenever possible.

This workflow implies that at the start, only a small subset of Go is supported as input. After feedback from the simulation and re-evaluation phases is gathered the supported subset can grow and the program can become more powerful. Alternatively the current implementation can be optimized first (e.g. in regards of hardware usage).

5. Assessment of implemented concept and exploration of limits by simulation and analysis:

After reaching an implementation goal in the previous phase this step will analyze the current implementation. The goal is to verify the functionality of the current state of the tool and explore the limits of the program.

Firstly, feature exhausting input Go code (i.e inputs that will cover all features or every newly implemented features of the current solution) is used to generate example VHDL code. Afterwards the VHDL output will be put to test in a testbench using ModelSim. Simulations allow to first look at the generated hardware as a black box and whenever there are problems ModelSim makes it possible to look deep into the system by observing single signals at certain timestamps. This process is used to ensure correct and desired functionality of generated hardware. Note

that the generated output makes it possible to even analyze some timing violations by including non-synthesizable VHDL wait statements on relevant assignment operations.

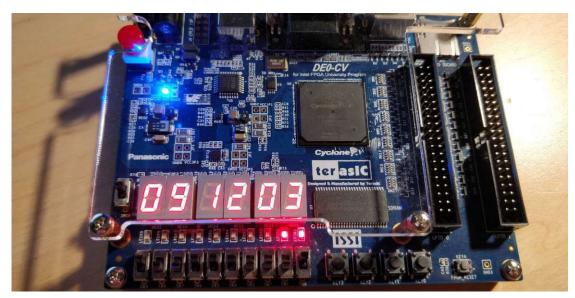

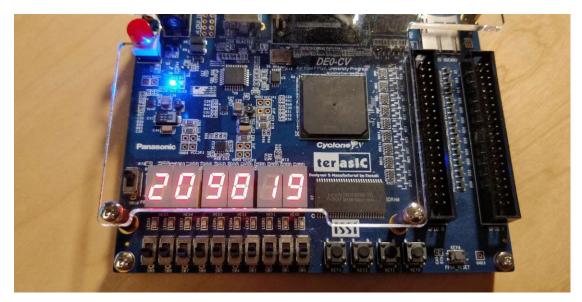

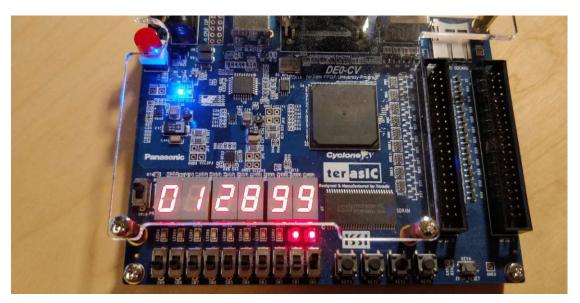

After satisfactory validation of the tool some outputs will be tested on actual hardware. In this case, the used synthesis tool will be Quartus [13] and the target development board will be a Terasic DE0-CV [14] board. This will be done to physically verify the results of the simulation and ensure the usefulness of the developed high-level synthesis tool go2async.

# 6. Optimization and Re-Evaluation:

In a last step before potentially circling back to the implementation phase, the current state of the tool will be re-evaluated. Solution concepts for found problems and limits of the tool are formed.

Based on results and findings of the simulation phase possible optimization ideas will arise. This thesis' work will mainly focus on generated hardware optimizations (e.g. hardware exhaustion of target FPGA) rather than optimizing the generation process itself.

Lastly, whenever problems are fixed and optimizations are completed, depending on the functionality satisfaction of go2async the next implementation step is decided. These are mainly the next to-be supported Go features which will be implemented in the next version of the tool.

# Technical Background

This chapter covers the state of the art and related technical topics regarding this thesis. Starting with the dissection of the title of this thesis the async part in go2async will be tackled first by reviewing problems of synchronous circuits and their asynchronous counterpart. The essence of this project - namely high-level synthesis tools - and similar programs are discussed before diving into the low-level backbone and the inner workings of this thesis' project. This introduces the 'click-element' segment of the title when literature about asynchronous pipelines is reviewed.

Complete the dissection of the thesis project name and Go reveals itself as a chosen programming language where 2 tells us that this certain language is transformed to something async(hronous). Lastly, this chapter looks at alternative language candidates for this thesis' project.

## 3.1Synchronous Circuits

Synchronous circuits make up the broadly established day-to-day hardware. Almost any purchased hardware has some clock signal in its specification which determines its operation speed. This type of circuit operates on a discrete time variable. Generally, the clock speed is linked to the maximal allowed depth of computation logic between two flip-flops. This is also known as the critical path in a circuit. That is the time a signal is allowed to travel through logic gates between two neighboring flip-flops without violating their setup and hold timings. Synchronous circuits have a centralized clock signal which governs the whole circuit. This is already one of the disadvantages of synchronous circuits as the clock is a single point of failure.

In this type of hardware the top speed is always only dependent on a single critical path even though this path might not even be the most active part of the hardware and the rest of a circuit allows narrower timings. This implies that synchronous circuits rely on

worst-case assumptions for their critical paths to ensure correctness at any time and circumstance. This includes internal and external assumptions. Worst-case assumptions are usually very pessimistic to cover (often rare) edge cases.

Another challenge bigger synchronous circuits face is managing their clock tree [15] especially in modern multiple power designs [16]. Simply using the same clock source in two different signal paths in a circuit means that this clock signal might arrive at slightly different times on two different circuit components. These two signals might merge paths at a later point in time. This time difference is called *clock skew*, which can cause unforeseen timing violations, if not properly considered.

Synchronous circuits generally have to bother with unnecessary high power usage because without special care the whole circuit is supplied with a toggling clock signal making the whole circuit stay active even though there might be only few active relevant computation paths. There are two types of power dissipation: Static and dynamic. Generally, static power dissipation comes from leakage current through transistors whereas dynamic power dissipation comes from switching current. Thus, dynamic power dissipation plays a big part for synchronous circuits. Popular low power design techniques are:

- Clock gating: Ability to turn off the clock for parts of the circuit [17, 18].

- Power gating: Ability to turn off power for parts of the circuit [18].

- Variable voltage: Ability do supply lower voltage for lower performance parts of a circuit [19].

Synchronous circuits' very restricted adaptability to physical properties and technology migration are disadvantageous for them. Whenever parts of a synchronous design change, the whole circuit needs to be re-evaluated. Especially the critical path analysis has to be done after every change. This also implies that it is generally not trivially possible to use old and slower (albeit already verified) parts of hardware in new designs.

## 3.2**Asynchronous Circuits**

Asynchronous circuits are self-timed and operate under a continuous time variable. Instead of pessimistic timing assumptions for calculations between two flip-flops this type of design requires calculation-complete detection to transfer valid data from one node to another. Asynchronous circuits solve all previously mentioned problems of their synchronous counterpart:

The speed is not dependent on some critical path. There are no scalability issues since there is no centralized control unit. The major (dynamic) power usage occurs only in the actively computing path. Asynchronous circuits are more-or-less plug-and-play and thus compatible with similarly behaving hardware by design. However, they have their own disadvantages as they require more delicate care and much more attention to detail

regarding the dynamic state of the circuit to avoid potential hazards. Additionally, each component of asynchronous circuits operates at the same time. The lack of discrete time steps make it impossible to verify every possible behavior.

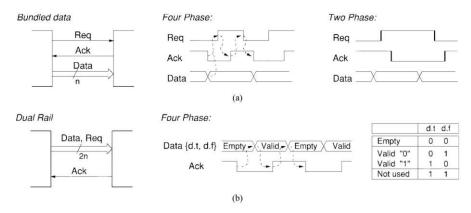

There are two big asynchronous design principles (and three protocols) which can also be seen in Fig. 3.1:

Figure 3.1: The three asynchronous protocols used in practical asynchronous designs: (a) the four-phase and the two-phase bundled data protocols and (b) the four-phase dual-rail protocol. ([4], Fig. 6.)

# • Bundled data/Bounded delay

Just like synchronous designs these asynchronous circuits use timing information in some way to detect phase changes. The backbone of this approach is a handshaking protocol between a source of information and an information consuming sink. The goal is to ensure proper coordination between entities.

Typically, handshakes are initiated by the source to signal the sink that data is stable and ready to be consumed. The sink is able to communicate consumption completeness. The participating signals are usually request and acknowledgement signals with an accompanying data vector. In the general case, the data vector and request signal travel from a source to a sink at the same time. The data however potentially traverses some processing circuit. A delay element has to be inserted into the request signal path which at least matches the worst-case timing behavior of the computation logic to remove a race condition. Recall that the request signal notifies the sink that the data is stable and ready. These delays can be achieved by e.g. inserting inverter chains. The arriving request signal is typically used as a trigger to capture the data vector in a latch or flip-flop on the sink side of the communication channel. After the sink captured the request signal it answers with a corresponding acknowledgement which triggers the next phase on the source side (i.e. ready for more data). These types of circuits need special care during the physical design to ensure timing constraints.

Handshake protocols can either be a four-phase or two-phase protocol. The fourphase (Return-To-Zero (RTZ)) handshake protocol only detects incoming events on certain input state changes (depending on the initial state) and requires handshaking signals to return to an initial state before triggering a new event (see Fig. 3.1 (a) in the middle).

The two-phase (Non-Return-To-Zero (NRTZ)) handshake protocol listens for input state changes only. Thus two-phase handshakes are simply faster but require additional hardware to track the current phase state (see Fig. 3.1 (a) on the right)).

# (Quasi-)Delay insensitive

This design method does not need a sense of time. Instead of using (delayed) handshakes the data vector between a sender and receiver gets encoded which requires additional wires per bit sent. This eliminates the need of a request signal. The simplest case is the 1 bit to 2 wires dual-rail encoding but it is possible to get different levels of complexity and performance by using m-of-n codes [20] (see Fig. 3.1 (b)).

In principle this method works by introducing valid and invalid (NULL or empty) states for the data vector. The receiving side needs data validity (e.g. no NULL or empty states) or completion detection. This can be done by expecting NULL-states (empty information) on each data-rail after single transmissions. The next set of inputs are only accepted after each rail of an incoming data vector returns to an invalid state before each rail gets to a new valid state. This behavior is similar to the RTZ pattern of four-phase handshaking and cannot be avoided here. While these types of circuits are associated with high robustness they show substantial area overhead [21].

It is obvious that handling communication channels between components individually gets very complex for big circuits. The need of control logic for each calculation to ensure ordered operation is simply solved by placing flip-flops in the synchronous counterpart. This makes hardware design for asynchronous circuits unbearable without tool assistance. The control logic of asynchronous circuits leads to large area usage [4].

Additionally, common Computer Aided Design (CAD) tools and most FPGAs are optimized with synchronized circuits in mind, leaving the development of asynchronous hardware even more disadvantageous [22].

Asynchronous circuits have caught the attention of hardware designers working on eventdriven circuits. Neuromorphic computing requires the processing of time and space sparse spikes which make this type of circuit very useful and employ a more natural control flow [23]. IBM's TrueNorth [7] and Intel's Loihi [8] are example projects which show the usefulness of deploying asynchronous circuits to create power-efficient and scalable Spiking Neural Networks (SNNs).

## 3.3 **High-Level Synthesis Tools**

The everlasting need for ever more computation power is an endless challenge for the computer industry. An obvious way to tackle this problem on systems that support software execution is to make the heart of the system, the CPU, better and faster. One could also use special acceleration hardware for specific tasks (e.g. Graphics Processing Units (GPUs)) or get rid of the performance loss that software execution systems introduce by designing special circuits for specific applications (also known as ASICs).

While the hardware optimization approach seems appealing, it introduces its own huge overhead, especially in its verification process. Hardware needs to be bug free when it gets to the market, since there usually is no way to fix bugs in the field in an efficient way. Additionally, creating hardware requires highly educated and trained staff. Since hardware solutions are economically risky, hard and very expensive [24], custom hardware designs are only feasible if large quantities are demanded.

An easier and less risky approach to this challenge is using simulation and FPGAs for prototyping. This creates a dynamic workflow by using HDLs (e.g. VHDL, Verilog) which can be used to create simulatable virtual prototypes. After successfully testing a virtual only prototype this approach allows to load the described hardware into an FPGA where it can be physically verified. However, this design flow still requires specially trained personnel and does not get rid of the extensive verification effort.

This is where high-level synthesis tools come into play. These tools are the interface between software and hardware description. They allow untrained personnel to create hardware without knowing anything about hardware design and enable them to quickly achieve satisfying results. In general, an HLS tool takes some standard software code and tries to generate hardware in form of an HDL. The supported inputs are usually subsets of known software programming languages or can be graphical (e.g. flowcharts).

#### 3.3.1 Synchronous High-Level Synthesis

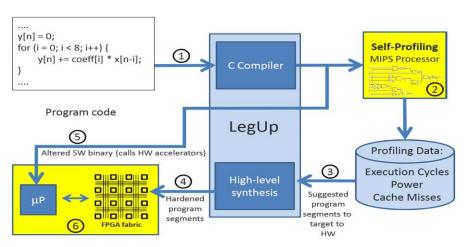

A commercially active HLS tool for synchronous circuits is LegUp [25] (acquired by Microchip[26] also known as SmartHLS). LegUp's design flow can be seen in Fig. 3.2.

LegUp synthesizes a processor/accelerator hybrid system. This program takes C code inputs and generates Verilog HDL. Without intervention the software runs on a soft-core MIPS processor on an FPGA. LegUp contains a self-profiler which is able to identify parts in the code that could benefit from a hardware implementation. A software programmer can then mark sections in the input code that should be hardware accelerated. LegUp maps C code to an HDL with the help of LLVM Intermediate Representation (IR) [27] instructions. A C statement might generate more than one IR instructions. These can directly be synthesized in an HDL. This allows the tool to create hardware accelerators for specific parts of the input software. The result is hardware on an FPGA where unmarked code will run normally on the given MIPS processor while marked code is hardware accelerated.

Figure 3.2: Design flow with LegUp. ([25], Fig. 1.)

#### 3.3.2 Asynchronous High-Level Synthesis

In the world of asynchronous circuits many approaches for high-level synthesis, mainly developed by universities, have been proposed in the past. Two big classes of asynchronous HLS are trending. The first being syntax directed translation and second being desynchronization. Syntax directed translation is the most commonly used. These tools essentially perform a one-to-one mapping of the syntax-tree of the input source into corresponding handshake structure components [28].

A concrete example of a syntax directed translation tool is Fluid [29]. This tool basically transforms C input code into an HDL with the help of LLVM IR [27] intructions and Control Flow Graphs (CFGs). The result is a bundled data circuit implementing fourphase handshakes using Muller-C elements [30].

De-synchronization aims as the name implies to convert a synthesized synchronous circuit into an equivalent asynchronous sibling. This is done by employing specific transformation rules for known structures. This method may not enable all advantages of asynchronous circuits but results in a circuit that has the typical asynchronous power-saving properties avoiding unnecessary power loss in inactive calculation paths and makes the circuit less prone to variability [28, 31].

## 3.4 Asynchronous Pipelines

Pipelining is the essence of high-performance circuits. It vastly improves throughput and parallelism of designed hardware. Synchronous circuits have a rather straight-forward approach to this technique. A simple way is to just split up big computation hardware into so called pipeline-stages which perform simple or parts of complex calculations in each of the created stages. If this process is executed on the critical path it may enable a synchronous circuit to run on a higher clock frequency [32].

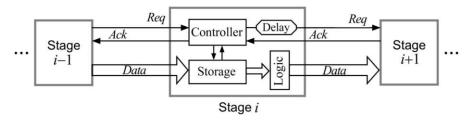

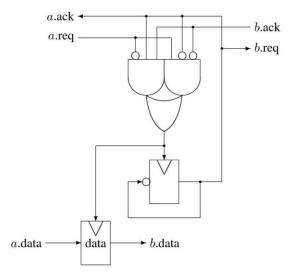

For asynchronous circuits this technique is more complicated. A recent investigation of asynchronous pipeline circuits based on bundled-data encoding [23] lists three big 2-phase handshaking protocols: Micropipelines, Mousetrap and Click. Fig. 3.3 shows an abstract view on asynchronous pipelines in linear form (e.g. no forks and joins). Consecutive pipeline stages communicate via handshake channels, usually consisting of Req(uest) and Ack(nowledgement) signals plus a data vector. In each stage a controller handles storage containers and coordinates the handshake signal. The delay in the outgoing Req(uest) signal path has to match the worst-case timing of the optional logic applied on the outgoing data path [23].

Figure 3.3: An abstract structure of a linear asynchronous pipeline. ([23], Fig. 1)

#### 3.4.1 Micropipelines

One of the first big and classic asynchronous circuits was deployed using Micropipelines [33] which were introduced with Sutherland's Turing Award lecture in 1988. The backbone control of this circuit is the well-known Muller pipeline based on Muller C-elements [30, 9. Also known as C-gate, it is a latch that has a state holding property. It changes its output if and only if all its inputs reach the same state. This makes C-gates very useful for synchronizing signal transitions in contrast to an AND-gate whose output is HIGH if and only if all its inputs are HIGH and puts its output to LOW if at least one of its inputs is LOW.

The drawback of this design is that C-elements are usually not supported by standard cell libraries and thus need custom implementations with special care. Research on how to implement hazard-free Muller Gates on common Lookup Table (LUT) based FPGAs can be found in [34, 35].

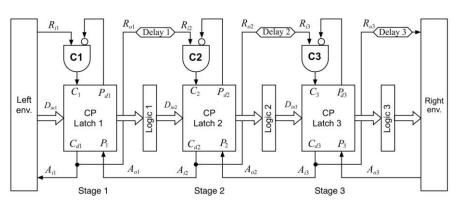

An illustration of the workings of the Mircopipeline with data processing can be found in Fig. 3.4. Each stage has a R(equest) input and an A(cknowledgment) output. Note that ack-signals need to be inverted such that phase changes occur correctly. This gives the circuit an oscillating behavior. The delay has to match the worst-case behavior of the inner-stage control and logic as is usual for bundled-data circuits. The event controlling latch is an unconventional capture-pass register. The input signals C(apture) and P(ass) of the latch have corresponding *done* signals which deliver output events after the latch is done with its action. State changes on C signals causes latches to capture data requiring transitions on P signals to make latches transparent again. [33].

Figure 3.4: 3-stage micropipeline circuit. ([23], Fig. 5)

#### 3.4.2 Mousetrap

Mousetrap [36] (minimal-overhead ultra-high-speed transition-signaling asynchronous pipeline) aims to improve the performance of its predecessor Micropipelines by simplifying the control of handshakes and thus significantly shortening the critical path. Additionally, Mousetrap manages to mainly use standard components (latches and XNORs) which makes this approach very convenient for automated designs or FPGA implementations. However, for non-linear pipeline structures (fork, joins) this pipeline design needs a fall-back to the unfortunate C-elements to synchronize diverged paths back to a single line.

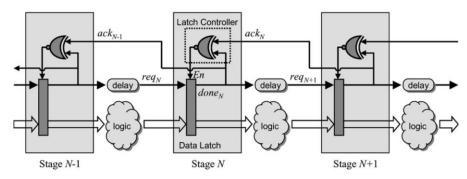

Figure 3.5: MOUSETRAP pipeline with logic processing. ([36], Fig. 4.)

The workings of this design scheme can be seen in Fig. 3.5. As is typical for the bundled data scheme the request signal needs to be delayed such that the data (logic) path successfully arrives at the next stage before the request signal does. XNOR gates are used to create the En(able) signal for the data latches. Even though the event generation behavior is similar to micropipeline's capture-pass register this approach allows the usage of more conventional single-rail blocks in the data-path as is standard for synchronous circuits according to [36].

#### Click-Elements 3.4.3

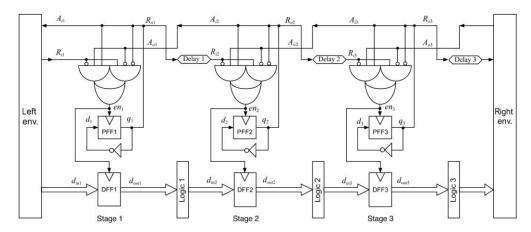

The click-elements project's goal was to improve on Mousetrap's shortfalls. In particular they managed to get entirely rid of C-elements and latches that are required in some control and data paths. Instead this design uses edge triggered flip-flops as data storage elements and also for the control circuits. The name *click* derives from the generation of pseudo-clock signals for the used flip-flops as this pipeline style also tries to mimic synchronous circuits as well as possible. In addition, this allows conventional tools to perform optimizations which usually cannot be done on asynchronous circuits. Clickelement circuits operate near the speed of Mousetrap circuits [6]. The fact that only standard library components are required makes this type of asynchronous pipeline especially convenient for FPGA implementations.

Figure 3.6: A 3-stage pipeline circuit based on the Click template. ([23], Fig. 10)

Fig. 3.6 shows an example circuit based on click-elements. Each stage consists of a controller circuit made out of simple standard library gates only. The control circuit generates a click-signal which is used on the clock-input of the phase (P) and data (D) flip-flops (FF). The changing edge of the control circuit signals a phase change of the handshake state. In the data path, this leads to the capture of the new output of the previous state whereas the state of the phase is simply encoded by inverting the output of the phase flip-flop. The controller essentially implements an arbitrary Boolean function which allows this pipeline scheme to deploy complex pipeline structures. This allows click-elements to mimic the functionality of C-elements if needed [6, 23].

Remarkably, it is possible to make these types of circuits optionally and easily synchronous and scan-testable. This allows for very convenient debugging of single states and stages of this type of asynchronously pipelined circuit which is normally a cumbersome task for this type of hardware. It can be done by OR-type gating a clock signal into the control circuit and adding a multiplexer in the feedback of the phase flip-flop which governs the scan feature. An example can be seen in Fig. 3.7 [6].

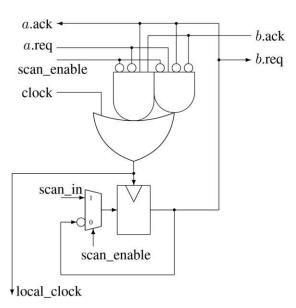

Figure 3.7: Scan-testable control circuit of Click pipeline stage ([6], Figure 18.)

#### 3.5 Work on Click-Elements

Click-elements are the obvious choice for asynchronous HDL implementations on FPGAs. Most importantly, they do not need C-elements and thus are just more convenient to realize. Additionally, they near the performance of Mousetrap [6]. This thesis continues reviewing work done on click-elements.

#### 3.5.1An Asynchronous Loop Structure Based on Click-Elements

An asynchronous loop structure based on click-elements is presented in [37]. An eight-bit Micro-Control Unit (MCU) was implemented with the aim to verify the loop structures based on click-elements. The designed circuit was simulated and compared against a functionally equivalent synchronous counterpart.

The built MCUs successfully delivered the correct results. On one hand, the performance analysis of the asynchronous version showed a substantially larger use of Logic Element (LE)s than the synchronous counterpart (189%). On the other hand, for the same instructions the asynchronous circuit had 37,5% less working time and it was found that it consumed dramatically less power.

#### Low Power Asynchronous RISC-V Processor 3.5.2

An FPGA implementation of the Click-based RISC-V Processor is shown in [38]. Li et al. realized an asynchronous RISC-V processor as well as a synchronous one with the same architecture on the same FPGA. By using RISC-V test-tools they verified both implemented CPUs.

To obtain power consumption data, the synthesis tool Vivado is used. As expected for asynchronous circuits, the result shows the asynchronous processor having up to 3x lower dynamic power consumption than synchronous core versions. On average a 200MHz synchronous implementation is 15% faster. However, the adaptive pipeline of the asynchronous design can have the advantage on test cases with few Load/Store operations like in the executed GCD test.

#### 3.5.3 Async Click-library

The contribution of [9] includes the realization of the findings of the click-element proposal in [6] with some additional ideas. The implementation is based on token rings. This work provides FPGA-implementations of click-element pipeline structures in VHDL which can be found in [10]. The implemented structures include the useful components: Register. Join, Fork, Merge, MUX, DEMUX and Function Block. These elements allow to create the functionality any typical software program can do in hardware.

The implemented components have a consistent interface consisting of in/out handshakes plus a data vector, allowing to conveniently link them together in a block-like fashion as needed. The Function Block needs special care since the delay of the outgoing handshake request signal has to match the block's combinational circuit. This is done by following the guidelines of [39] which will be relevant for this thesis' work as well.

So-called peephole optimizations reduce hardware costs by combining certain common handshake components such as Register + Fork which are needed by for-loops [9].

#### 3.6 Conclusion of Pipeline Findings

In addition to click-elements being the obvious choice for this project, the click structure implementions of [10] are already functionally verified and successfully tested in simulations as well as on actual FPGA boards by the authors. Thus, this pipeline structure is even more useful and convenient for this thesis. Consequently this GitHub repository's work will be at the core of go2async. The example circuits (e.g. Greatest Common Divisor (GCD)) presented in [9] whose implementations can also be found in [10] will act as references for the results of this thesis' project. First glances at the async-click library allow this project to form ideas for the automatic generation of such structures.

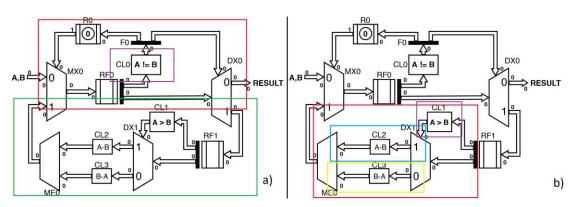

Fig. 3.8 is a colored version of the schematic of the GCD circuit presented in [9]. The GCD of two input numbers (A, B) is calculated by alternatively subtracting the smaller variable from the bigger one. The loop (and algorithm) ends if the two variables are equal. In this case, either value of both variables can be used as result of the GCD calculation. Conveniently, this circuit contains most important programming structures.

The colored outlines are common program structures. In a) a for-loop is marked. In [9, 10 a for-loop basically consists of a path controlling part (red) and a body (green). The condition component is highlighted in purple. In b) an if-statement is marked. It also

Figure 3.8: Schematic of the GCD circuit. a) marks loop-flow-control (red), condition (purple) and body of the for-loop. b) marks condition (purple) and if-flow-control (red) of an if-statement as well as then (blue) and else (yellow) paths. (Adapted from 9, Fig. 14.)

consists of a path controlling part marked in red. The condition components (purple) are highlighted as well. The bodies are marked in yellow (then-path) and blue (else-path). The GCD circuit from Fig. 3.8 will be more thoroughly discussed in Section 4.2.3.

As is usual for asynchronous circuits it is very cumbersome to manually describe such circuits in an HDL. However, the presence of common structures makes it seem possible to implement a syntax-directed translation as mentioned in section 3.3 and thus automate the generation of click-element circuits with the help of e.g. ASTs. This will be more thoroughly analyzed and discussed in Chapter 4.

#### 3.7 Programming Language Candidates

As previously mentioned this project aims to implement an HLS tool that deploys a syntax-directed translation. One way to tackle this is by requiring the code parser to abstractly represent the input code syntax. An AST is an example of an abstract syntax representation usual code-parsers are able to generate. This enables mapping of AST-nodes to the desired output format. An ideal language candidate would be a commonly known programming language since the core idea of HLS tools is to allow software-programmers to create hardware. Thus a well-known language is preferred whereas self-made or proprietary input languages are not an option.

Preferably, language candidates have following properties:

1. There is a parser for the language that is able to create an AST from source code.

This is the most important property a syntax-directed translation relies on.

2. The parser of the language is self-hosting.

That means the parser is written in the same language as it parses. This property is very advantageous because it would make the development more convenient, since there is no switching between two languages for development and hardware generation.

## 3. The language is simple.

A simple language that is easy to parse and does not allow many alternative variants of valid syntax for the same code is also preferred. This would get rid of the requirement to implement the same output for various inputs that described the same function anyway.

## 4. The language is well-known or similar to well-known ones.

This enables a lot of potential users and especially addresses the big selling points of HLS tools whose goal it is to enable hardware design without much knowledge about the design process.

With these three requirements in mind the following three programming language are analyzed briefly: Python, Rust and Golang.

#### Python 3.7.1

Python [40] is an interpreted and dynamically typed programming language which was found in 1991. It is often described as a scripting language. This allows Python programs to skip the compilation step and thus make the edit-test-debug cycle fast. A Python script is simply executed and in case of errors the interpreter raises an exception or prints a stack-trace. Python is also known for its Rapid Application Development (RAD) ability and the short code it requires for tasks in comparison to other languages [41]. According to [42] Python was the #2 used programming language in 2022 on GitHub.

As wished, the Python interpreter can parse Python itself and process Python syntax grammar. However the dynamic typing is rather unpleasant. For instance Python allows to reassign variables with entirely different types later in the code. This property would require additional effort if used in this HLS tool. Additionally, the syntax is relatively complex which is rather disadvantageous with this project's 'start small get bigger' implementation style.

#### 3.7.2 Rust

The Rust programming language [43] was first announced in 2010 by Mozilla. [42] lists Rust as one of the fastest rising languages in recent times. It is most known for its memory and type safety enforcement by employing special rules for dealing with references without requiring a garbage collector. Rust is strongly and statically typed. Thus, types must be known at compilation time and cannot change mid-program. Rust defines built-in types with predefined sizes. This type knowledge is useful for hardware

generation since data-vectors between handshake components have constant sizes once synthesized.

Rust also provides a Rust compiler and an explanation of its AST. However, Rust is a very complex and new language whose concepts are not widely understood. It also allows features from functional programming whose translations to hardware are not feasible for the scope of this work.

#### 3.7.3Golang

Go is a compiled programming language created by Google with the first stable version in 2012 [12]. The goal of the creators was to create a language that is lightweight, easy to use and easy to parse. The language is statically typed. It also entails predefined types. An analysis of programming languages deemed Go as a potential super-popular language [44]. The compiled code uses a garbage collector.

Like the previous two languages Go ships with a self-hosting parser which is able to generate ASTs. As it turns out Go's clear, simple, and lightweight syntax makes this language a very suitable candidate for this project. The provided AST and parser are easy to work with. Go's simple code structures force specific coding styles which make even subsets of this language seem like ordinary Go code. This leads to few redundant translation mappings other input languages would require. Another nice feature is Go's machine independence. The compiler entirely handles different environments.

Note that the Go language features *goroutines*. This is a way to concurrently run code. Combining this with channels yields event-driven and asynchronous code behavior which could potentially be translated into asynchronous hardware as the channels' send/receive functionalities mimic handshaking behavior.

The simple syntax of Go, while providing rich functionality, makes this language the main choice for this project as long as no dynamically allocated memory is used.

# **Key Challenges** and Solution Concepts

This chapter extracts challenges and uncovers tasks required for the creation of this thesis' high-level synthesis tool go2async. Afterwards, rough solution concepts are drafted for the aforementioned problems. This chapter also explains the project-relevant ins and outs of the Go AST before drawing parallels to the click-library from [10]. The solution concepts will be ultimately tackled in the following implementation section of this thesis (Chapter 5).

#### 4.1 Key Challenges

In general, an HLS tool for asynchronous circuits has to address the following classes of challenges for the design of asynchronous hardware:

## 1. Timing and Hazard Analysis

The absence of a centralized clock in asynchronous circuits directly introduces additional complexity in timing analysis compared to their synchronous counterpart. It is necessary to eliminate the possibility of hazards such as glitches and race conditions for each computation path.

Moreover, complex calculation paths (e.g. forks and joins) and the use of unconventional synchronization elements (C-elements) might cause further problems (particularly on FPGAs) depending on the used asynchronous pipeline structures.

## 2. Protocol Design

Asynchronous circuits rely on handshaking or encoding protocols to ensure the proper order of calculations. The key is defining an efficient and reliable protocol that can handle complex data dependencies and path synchronization requirements. Furthermore, verifying the correctness of the deployed inter-component communication protocol is an additional huge challenge.

## 3. Productivity

Designing asynchronous circuits is cumbersome due to the complex analysis task and the lack of standardized design methods. This makes it challenging for hardware designers to develop asynchronous circuits.

## 4. Tool Support

Synchronous designs have received more attention in terms of tool support compared to their clock-less sibling. The lack of tools and support for asynchronous circuits can make timing analysis and optimization processes more tedious. Therefore, HLS tools for asynchronous circuits need to take extra care for their results to alleviate these challenges.

## 5. Hardware Design Automation

A system for the automated synthesis of asynchronous circuits must address all the aforementioned challenges. Such a system would significantly improve productivity, simplifying the complexity of asynchronous hardware design and even enabling untrained personnel to develop clock-less circuits. The automation process should be user-friendly to enable widespread usability.

## 6. Software Design

Lastly, a fresh implementation of an HLS tool is its own complex endeavor. Software projects require a well-defined specification and careful planning. Functional requirements should outline needed functionalities and features the resulting project must possess. Non-functional requirements (such as usability, reliability and scalability) ensure that a satisfying performance is met and allow a convenient way for future and further development. This should serve as the foundation to ensure that expectations are met.

#### 4.2 Solution Concepts

#### 4.2.1 Timing and Hazard Analysis & Protocol Design

As the title of this thesis already mentions, click-elements play a vital role in this thesis' project. This kind of asynchronous pipeline with the help of [6, 9] and the click-elements VHDL implementation of [10] allows go2async to solve the previously mentioned problems 1 & 2.

In more detail, the Click pipeline template defines three constraints that need to be satisfied for the correct operation of such circuits [6]:

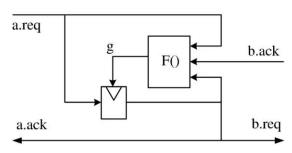

Figure 4.1: Click template two-phase pipeline implementation with feedback-loop based on flip-flop (adapted from [6], Figure 3.)

Figure 4.2: Click implementation of simple pipeline stage. ([6], Figure 2.)

- 1. The click pulse width generated by the control function circuit needs to be larger than the used registers require.

- 2. Input handshakes need to stay stable during an active clock phase.

- 3. Hazards such as glitches on handshake signals must be avoided.

The first problem can simply be solved by using common static timing analysis tools to verify whether this condition is met or not since the same verification is needed for synchronous circuits as well.

Fig. 4.1 and Fig. 4.2 show how the remaining constraints are overcome. The output of the flip-flop is fed back into the control circuit, therefore handshake signals are only allowed to toggle after the corresponding output handshake signal is stable. It is claimed that handshake signals are driven by flip-flops, thus these are safe and free from glitches [9].

There are no problems with race conditions because of the construction of the handshake control circuit. It can be verified that potential differences in arrival time of incoming handshake signals do not affect the operation of a circuit using the click template.

The deployed handshaking protocol of the click template is of the two-phase bundled data variant. The behavior of the pipeline design can be described as two-phase token-rings with any number of tokens (often just a single one) where data (a token) is latched from previous pipeline stages and passed to successor stages. Complex pipeline stages are handled by designing a specific control circuit (see F() in Fig. 4.1).

#### 4.2.2Productivity & Tool Support

These two key challenges are at the core of this thesis' project. Productivity gains for asynchronous circuit designs are already vastly enhanced by using the predefined and verified asynchronous pipeline implementations such as the click-library [10]. However, it is still necessary to manually wire all handshakes and to keep track of parallel computation paths. This is obviously a very time consuming and extremely complex process which scales with the size of the target circuit. Maintainability problems will easily arise as an additional challenge.

This thesis' project will not only further improve productivity by completely removing and abstracting the time-consuming process of VHDL implementations, but also take away the need for timing analysis and optimization tools as go2async will deploy its own design methodologies for certain computations.

The use of an easy and widespread user interface for hardware creation is key here. In this case the target group are software developers who aim to speed up processes by utilizing custom hardware. Go2async enables them to do that more conveniently and exploit potential benefits that come with asynchronous hardware. As mentioned in the previous chapter, this project opts to use the rising (C-like) programming language Go and makes use of the light weight parser and its methods to create the target designs.

#### 4.2.3 Hardware Design Automation

The solution concept for this challenge requires researching the available resources, namely the target programming language (Go) and the click-library [10], and looking for patterns. This project aims to develop a syntax-directed translation from Go to VHDL, thus reviewing the Go language and its AST is the next obvious step. Afterwards, repeating patterns in the click-library ([10]) will be searched for.

### The Initially Supported Go Language Features and AST

This thesis focuses on Go language features that are relevant for the solution concept and will be supported by the resulting HLS tool. In principle, a valid Go program only requires some package name and a function (main function as an entry point for executables). Go functions are declared with the keyword func followed by the function

name, function parameters in parentheses and the function result type. The result types can be a named list just like the parameters. The function body in curly brackets contains Go statements. The project only supports Go functions that contain exactly one return statement to avoid unnecessary complexity during translation. Every function can be converted to such form anyway. The accepted Go subset should at least include functions, assignments, if-statements, for-loops, and binary expressions.

The initial solution supports at least the integer basic types as well as bool. In particular this includes byte, int, int8, int16, int32, int64, and their unsigned counterpart. In addition, it is able to also work with arrays, so that useful and powerful programs can be written as well.

The initial concept considers simple Go input code only because many Go features (especially syntax sugars) are expected to migrate without big complications into future versions once basic implementations work successfully. For instance, if binary expressions are well translated into hardware by go2async, a sum of three numbers will not be a big problem since this particular example can be written in two binary expressions. Additionally, if-statements and for-loops only consider Boolean binary expressions as condition expressions for further simplicity.

```

package goexamples

2

func sum(a, b int) int {

3

4

а

+ b

5

7

return a

}

```

Listing 4.1: Simple sum function in Go.

Listing 4.1 depicts a short and simple example Go code implementing a sum function for two integers. In Fig. 4.3 a slightly simplified AST of the sum function code can be seen. The figure omits additional contents of the Go AST such as source file information since they are not important in the context of this thesis. In general, a node's name, or in case of an array, the array index is followed by a semicolon. After that, the node type's name is written in angle brackets. The Go package name prefix of the node pointer types (\*ast.) and type hierarchy relations are dropped for readability.

The relevant root node of the shown Go AST in Fig. 4.3 is *Decls*. This node contains an array of all declarations in the Go example which contains exactly one function. The function declaration contains the expected name ("sum"), parameter fields, and results fields. Note that the parameters are defined of type *Ident* (identifier) because the parameters are named, as opposed to the function result type, which is simply an integer (type int). The function declaration also contains a Body which is an array of Stmt (statements). Similar arrays of statements also occur in trees of loop bodies, if-

Figure 4.3: Simplified Go AST of the sum function from Listing 4.1

statement bodies (then and else paths) as well as in general code blocks (code specifically bracketed by additional curly brackets). Such commonly occurring AST structures are very convenient for future processing purposes.

The body from Listing 4.1 consists of two statements, namely an assign statement and a return statement (respectively AssignStmt and ReturnStmt in the tree). As usual an assign statement has a Left-Hand Size (LHS) and a Right-Hand Size (RHS). The RHS resolves as a binary expression (BinaryExpr) of the identifiers a and b with the +operation. The return statement simply contains the identifier a.

If-statements and for-loops are represented in the AST as constructs that contain a condition expression that resolves to a Boolean value and a body containing an array of Stmt just like FuncDecl. As already mentioned, the thesis' initial solution concept focuses on simple binary expressions for the condition expression. For-loop statements with "for clauses" (init statement, exit condition, and post statement) which are usually used to increment a counter variable (often i), as well as if-conditions with assignments are not supported.

## The Click-library

The thesis focuses on and analyzes the construction of the click-structures from [9, 10]. For this purpose the GCD example circuit from Fig. 3.8 is used. Note that every arrow

depicts a two-phase handshake plus data from one element to another. The previous chapter already explained parts of this.

Each component has one or more input channels (signals for handshakes and data) and one or more output channels. Every component implements their own inner handshake and data-control (see F() in Fig. 4.1). There are many important click-element pipeline structures implemented in [10] (for instance register, fork, MUX, ...). Following relevant big structures consist of and rely on one or more pipeline components:

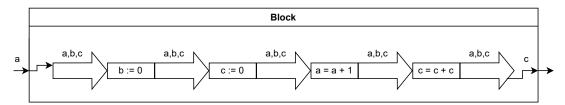

#### 1. Statement

A statement is simply a function structure that executes some operation(s) on its input(s) and outputs the results. Remarkably, this component has non-constant handshake delays, as opposed to all the other structures, because the handshake management of this component depends on the used operation. For instance an addition requires larger logic and thus more time than an assignment statement. This time-delta has to be determined and dealt with in the handshake paths.

## 2. For-Loop

The for-loop in the example from Fig. 3.8 consists of an entry-multiplexer (MUX)  $MX\theta$ , a for-loop state register (with fork)  $RF\theta$ , a loop-condition component ( $CL\theta$ ), a condition register  $(R\theta)$ , and a loop-body. The body usually starts with a register but the example was optimized so that it was replaced with a Register-Fork combination (RF1) (the fork is actually part of the if-statement).

$MX\theta$  (in combination with  $R\theta$ ) governs whether the loop should get data from outside of the loop structure (e.g. by starting to process a new loop) or accept the input from inside the loop body. Either way, data is passed to  $RF\theta$  in which the loop state is stored. The register forks its output to CL0 and DX0. CL0 calculates the loop condition and forks its result again to  $MX\theta$  (over  $R\theta$  - this is explained in the next paragraph in more detail) and  $DX\theta$ . Depending on the loop condition result the loop either ends and outputs the current loop-state  $(R\theta)$  over  $DX\theta$ . In this case MX0 waits for new input from outside the loop. In the event that the loop condition allows the loop to continue,  $DX\theta$  outputs the data from  $RF\theta$  to the loop body for further processing until it arrives on the "1" input of  $MX\theta$  where this triggers a new loop process.

R0 is special. It is specifically marked with a "0" in a circle at its beginning state (see upper left component in Fig. 3.8) and operates on a different output phase than the rest of the circuit. This is required since a MUX in [10] only accepts inputs if each relevant request signal arrived (condition AND input paths). That means that when initially there is an incoming handshake on the 0-input of MX0it is only accepted if and only if the selector data is "0" and the request signal of the handshake channel from the selector path is also already high. In token-ring vocabulary this would translate to: There is a token at R0 at the beginning of the operation and bubbles everywhere else.

```

package goexamples

2

func GCD(a, b int) int {

3

for a != b /* a) purple */ {

// a) green

5

if a > b /* b) purple */ {

6

= a - b // b) blue

7

else {

8

b = b - a // b) yellow

9

10

11

}

return a

12

13

```

Listing 4.2: Golang implementation of a GCD algorithm.

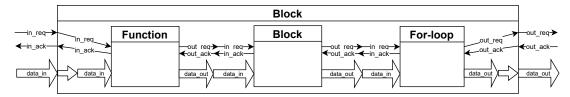

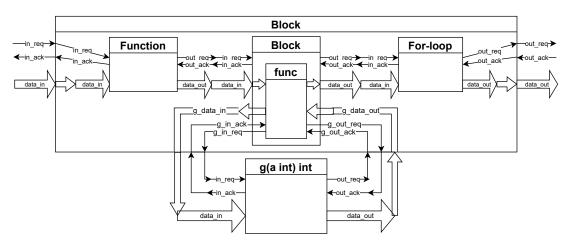

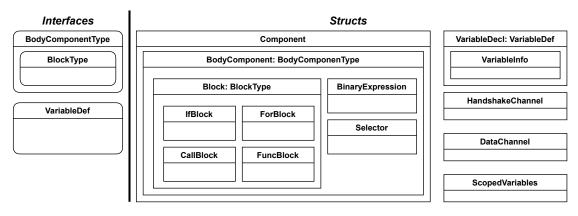

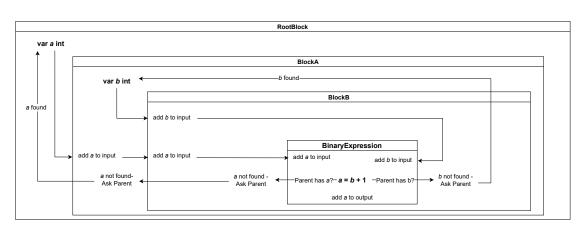

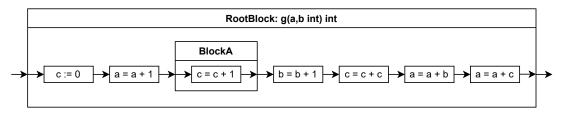

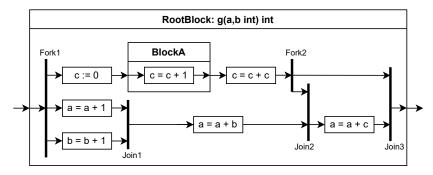

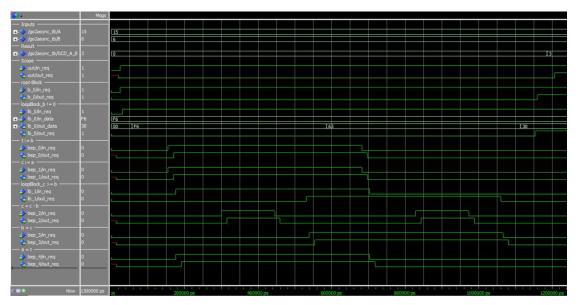

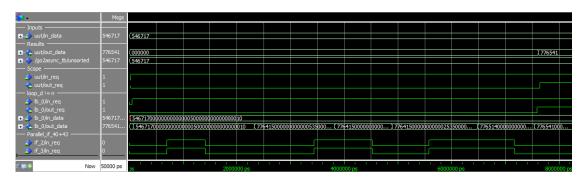

#### 3. If-Statement